# P1 Series

# P1013/P1022 embedded processors with advanced energy management

Energy Efficient Solutions by Freescale

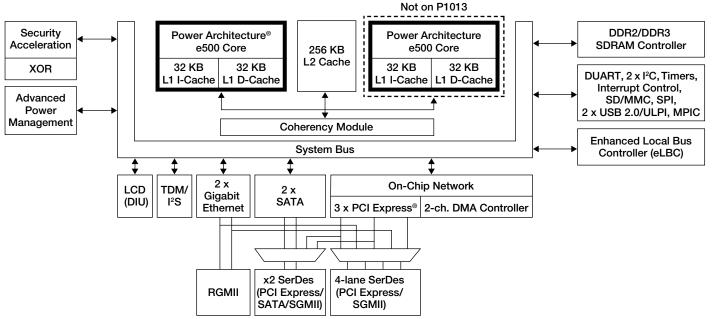

Freescale QorlQ communications platforms are the next-generation evolution of our leading PowerQUICC communications processors. The P1022 family of processors, a Freescale Energy-Efficient product solution, is designed to deliver complex application processing performance with exceptional feature integration and high-speed connectivity for IP networking and advanced media processing applications. It combines dual e500 processor cores, built on Power Architecture® technology, with enhanced system peripherals and interconnect technology to balance processor performance with I/O system throughput. The P1022 processor includes advanced power and energy management features that enable developers to design next-generation embedded Internet media processing applications with energy efficiency levels under the environmental and governmental energy regulatory requirements. The P1013 single-core processor includes

the same family of system peripherals, interconnect technology and advanced power and energy management features.

#### **Highlights**

#### **Dual-Core Processing**

The pace of technology development, spurred by the Internet and ubiquitous connectivity, is putting additional challenges on design engineers building state-of-the-art embedded appliances or equipment. The P1022 provides the designer exceptional flexibility for leveraging symmetric and asymmetric multiprocessing strategies to reach nearly two gigahertz equivalent single-core performance in ultra-low-power envelopes. Equally important are the robust operating systems and tool support to streamline designers' adoption of dual-core processing available on the P1022 through Freescale and Freescale partners.

#### **High-Speed Connectivity**

Freescale's P1022 processor is positioned to offer a wide range of high-speed connectivity options. The flexibility of the processor is due to highly integrated speed- and latencyoptimized technology. It is a highly scalable processor designed to handle complex, computationally demanding processing tasks with ease. The P1022 processor includes virtualized enhanced three-speed Ethernet with TCP/UDP/IP offload, direct FIFO mode for ASIC connectivity, SATA for local storage and support for three PCI Express® interface options. Moreover, the P1022 processor features a field-proven, next-generation memory controller and an optional hardware acceleration engine for encryption protocols and RAID processing.

## QorlQ P1022 and P1013 Block Diagram

#### System-Level Cost Saving

The P1022 processor's highly integrated architecture is designed to enhance performance and deliver system-level cost savings in a small board footprint. Key system-level peripherals include dual Gigabit Ethernet, dual USB 2.0, dual SATA, SD/ MMC and triple PCI Express interconnects. Furthermore, the P1022 integrates LCD controller, I2S audio and VoIP TDM interfaces for use in creating engaging human interfaces. Special care was taken to design the P1022 processor's pin locations for mounting on low-cost six layer PCBs. The P1022 is a full-featured, high-performance gigahertz processor that is designed to support fanless operation for power-sensitive applications.

### Advanced Energy-Efficient Modes

Balancing the performance requirements for powerful new networking- and Internetcentric applications, with the increasing concerns over energy consumption, is driving manufacturers to develop intelligent strategies for optimizing performance within specific energy budgets. This is a key challenge for the next-generation green embedded systems. The P1022 processor implements sophisticated power-saving modes for managing energy consumption in both dynamic and static power modes. These include the traditional nap, doze plus the jog (dynamic frequency scaling) and packetlossless deep-sleep modes. Designers may leverage these modes to efficiently match work accomplished with the correct level of energy consumed.

The combination of these features makes the P1022 processor an optimal embedded processing solution for Ethernet or PCI Express interworking applications, such as enterprise networking, industrial, storage, security and office automation applications. Examples include control plane processing, protocol processing, media processing while producing an engaging human machine interface.

#### **Key Features**

- Dual (P1022) or single (P1013) highperformance e500v2 cores built on Power Architecture technology

- o 36-bit physical addressing

- Double precision floating point support

- Signal processing engine (SPE) APU (auxiliary processing unit)

- 32 KB L1 instruction cache and 32 KB L1 data cache for each core

- 600 MHz to 1055 MHz core clock frequency

- 256 KB L2 cache with ECC, also configurable as SRAM and stashing memory

- 64-bit DDR2/DDR3 SDRAM memory controller with ECC support

- Two 10/100/1000 Mbps virtualized enhanced three-speed Ethernet controllers (eTSECs)

- TCP/IP acceleration and classification capabilities

- ∘ IEEE® 1588 support

- o Loseless flow control

- · RMII, RGMII, SGMII

- Integrated security engine (optional)

- Crypto algorithm support includes 3DES, AES, RSA/ECC, MD5/SHA, ARC4, Kasumi, Snow 3G and FIPS deterministic RNG

- Single pass encryption/message authentication for common security protocols (IPsec, SSL, SRTP, WiMAX)

- XOR acceleration

- High-speed interfaces (not all available simultaneously)

- Six SerDes lanes (multiplexed across controllers)

- One x4 and two x1 PCI Express interfaces

- o Two serial ATA (SATA) interfaces

- ∘ Two SGMII interfaces

- · Audio visual interfaces

- LCD interface supporting a display of 1280 x 1024P @ 60 Hz, 24 bits per pixel

- I<sup>2</sup>S interface with maximum sampling frequency of 192 kHz

- VoIP TDM interface

- Support for up to 128 channels

- Two High-Speed USB controllers (USB 2.0)

- Host and device support

- o Enhanced host controller interface (EHCI)

- ULPI interface to PHY

- Enhanced secure digital host controller (SD/MMC)

- · Serial peripheral interface

- Programmable interrupt controller (PIC) compliant with Open-PIC standard

- · Dual four-channel DMA controllers

- Dual I<sup>2</sup>C controllers, DUART, timers

- Enhanced local bus controller (eLBC)

- · Advanced power and energy management

- Low power operation

- Support for dynamic and static power management

- Doze, nap and sleep modes for dynamic power management

- Packet-lossless deep sleep: power removed from major portion of the chip

- PMC wake on: filtered LAN activity,

USB connection, GPIO, internal timer or external interrupt event

- Up to 87 general-purpose signals

- Available in extended temperature (optional)

- 689-pin TEPBGA package

Learn More:

For current information about Freescale products and documentation, please visit **freescale.com/QorlQ**.